前言

在做牛客的题时,发现基础题的第三题就是奇偶校验,可见奇偶校验是一个基础掌握的,之前在做UART时,也遇到奇偶校验,但那时没有用到奇偶校验,下面把奇偶校验整理一下

正文 一、 什么是奇偶校验首先要明确需要校验的数据,如8bit的:1101_0010,数据中有4个1,因此,在奇偶校验时,奇校验=1,偶校验=0

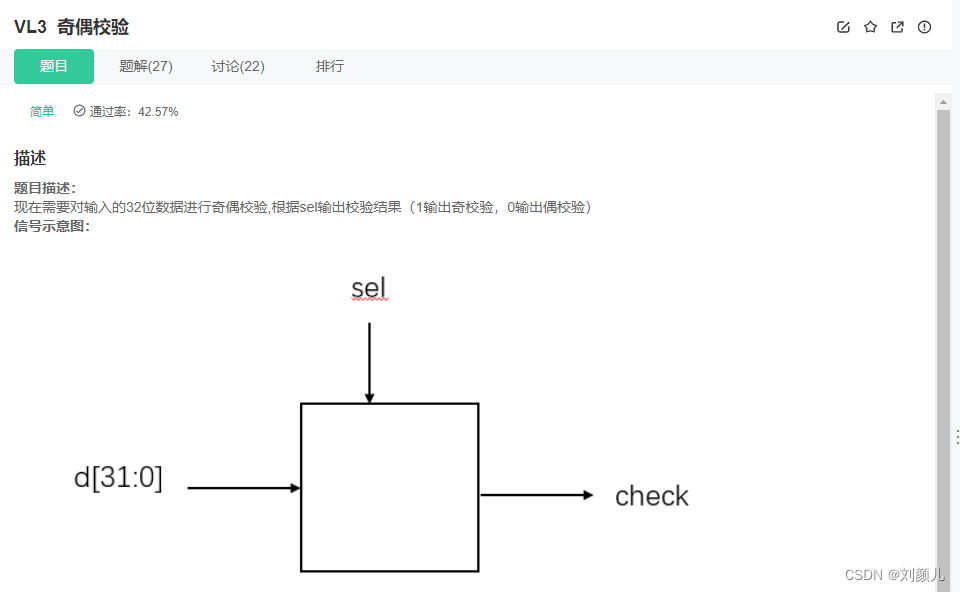

1.1 牛客题目看了上面的那一段描述,或许还是不知道奇偶校验是啥,能用来干嘛 那我们就直接开始看题

本题是对32位输入数据进行奇偶校验,题目中明确指出,奇校验=1,偶校验=0; 首先要知道这32位中有多少个1,应该怎么得到32位数据中有多少个1呢?除了常规使用累加求解,更加推荐使用下面的方法

要做奇偶校验,无非是想要知道原数据中的1个数是奇数个还是偶数个,我只关心个数的奇偶,不关心个数的具体值,因此回想到之前刷的HDLBits中的题,里面有用到类似的用法: HDLBits刷题–其他特点

// 为什么会提到奇偶校验

module top_module (

input [7:0] in,

output parity);

assign parity = ^in;

endmodule

HDLBits刷题-向量 我当时还疑惑,为什么提到奇偶校验

// 多位输入,分别用每位做:与、或、异或

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

//方法一

assign out_and = in[0] & in[1] & in[2] & in[3];

assign out_or = in[0] | in[1] | in[2] | in[3];

assign out_xor = in[0] ^ in[1] ^ in[2] ^ in[3];

//方法二

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmodule

于是使用相同的思路,我们可以得到32位数据中1的个数是奇数还是偶数 奇校验使用:odd_0 = ^ bus; 偶校验使用:even_1 = ~ odd_0; 注:奇偶校验重点是求出其中一个,另一个取反也能得到了

// 奇偶校验

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

wire even_1;// 偶校验

wire odd_0;// 奇校验

assign odd_0 = ^bus;

assign even_1 = ~odd_0;

assign check = (sel)?odd_0:even_1;

//*************code***********//

endmodule